1)上記2つのファイルを用いて、動作シミュレーションを行う。

注意事項

# run

だけ実行すると、CLKがあるような回路ではシミュレーションがとまらなくなる。

シミュレーションを止めるには

Execute -> interrupt もしくは Intrボタンを押す。

# run 時間

を使用するのが良い!

2)動作波形とVHDL4で説明した動作波形を比較して、同じであることを確かめる。

1) design_analyzerを起動し、addmul.vhdを読み込む。

2) クロック信号とその周期を指定する。

クロック入力端子をダブルクリックで選択し、

Attributes -> Clock -> Specify

Periodの欄に数値(たとえば50)を入力し、Apply

この数値がサイクルタイムの合成時の目標値になるので、面積重視で、サイクルタイムが長くてよい場合は大きな値を入れる。

逆に、サイクルタイムを小さくしたければ、小さな値をいれる。

3) 回路の合成を行う。

Tool -> Design Optimization

デフォルトの設定でOK

これで、回路が合成される。

4) 最小の動作サイクル時間を確認する。

Analysis -> report で

timingをチェックしてApply

表示されるリストで、

data arrival time はクリティカルパスのクロック立ち上がりエッジから次のFF入力までの遅延時間(Analysis -> Highlight -> Criticalpathの経路)

clock はクロック周期

library setup はFFの入力セットアップタイム

slack の値が設定に対するサイクルタイムの余裕である。したがって、設定サイクルタイムからslackを引けば、動作するサイクルタイムが求まる。

5)クロックの周期のターゲット値を1として、再合成する。

6)この時の最小の動作サイクル時間を確認する。

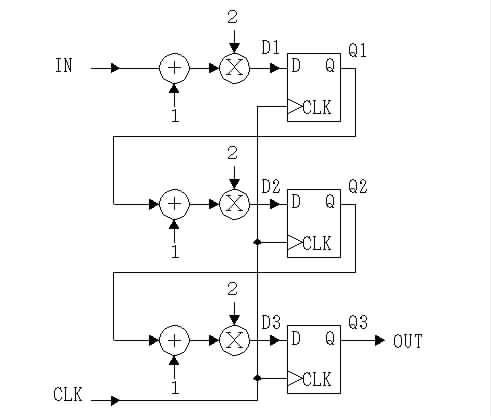

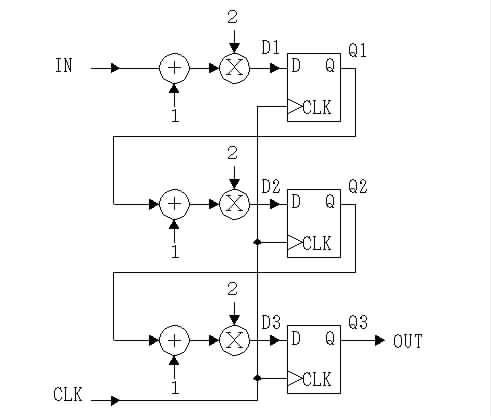

1) 回路のVHDL記述を作成せよ。

2) 上記入力INに毎サイクル連続に1,2,3,4,5を入力するテストベンチを作成せよ。

3) VSSにてデバッグし動作波形図を求めよ。

4) 面積最小の回路図を合成し、その最小動作サイクル時間を求めよ。

Periodの指定を十分大きくする(たとえば50)、面積のターゲットを0.00とする。

5) 最小のサイクル時間で動作する回路を合成し、その最小サイクル時間を求めよ。

Periodの指定を小さくする(たとえば1)、面積のターゲットを空欄にする。

以下のものを含むレポートを提出する。

1)作成した回路のVHDL記述

2)作成したテストベンチのVHDL記述

3)動作波形

4)面積最小合成時の回路図、面積、最小サイクル時間

5)最小サイクル時間合成時の回路図、面積、最小サイクル時間