そして回路ブロックを階層化させて大規模な回路を構築する。

琉球大学情報工学科 和田 知久

| 設計レベル(例:パソコン) | VHDLの記述レベル | |

|---|---|---|

| マザーボードと周辺機器(全体) | アーキテクチャレベル記述 | |

| マザーボード | ビフェビアレベル記述 | |

| Integrated Circuit | レジスタトランスファーレベル記述 | ここを学ぶ! |

| ロジックゲート | ストラクチャレベル |

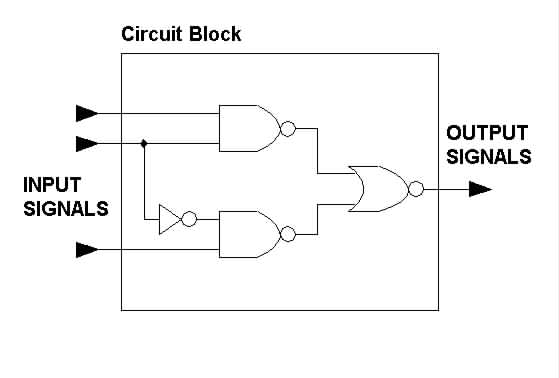

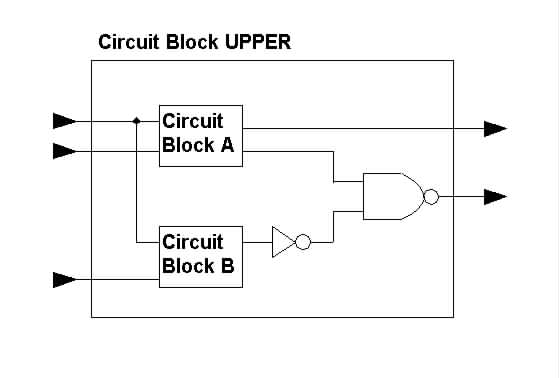

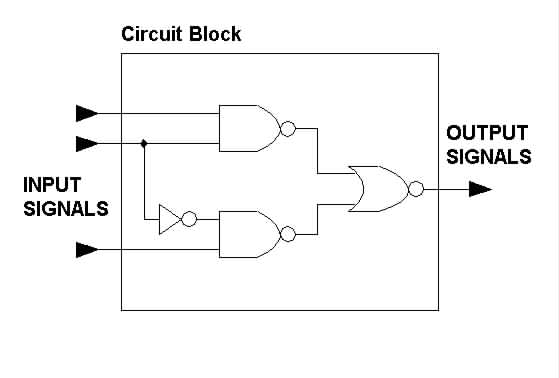

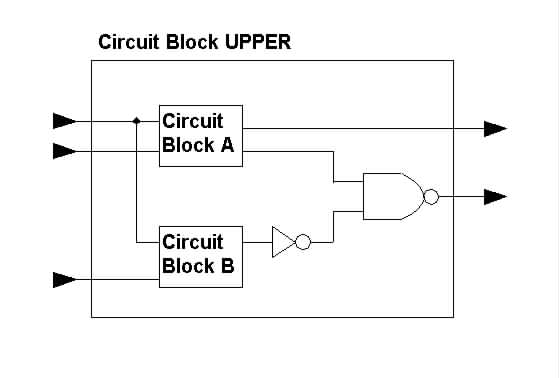

設計者が取り扱いやすい以下のような大きさの回路ブロックを設計する。

そして回路ブロックを階層化させて大規模な回路を構築する。

エンティティ宣言とアーキテクチャ宣言により回路ブロックを記述する。

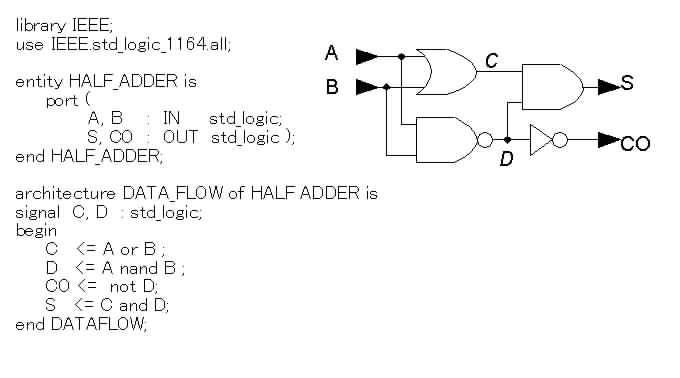

| library IEEE; use IEEE.std_logic_1164.all; |

ライブラリ宣言、STD_LOGICを使用する場合に必要 いつもSTD_LOGICを使用するのでいつも必要! |

| entity HALF_ADDER is | エンティティ宣言 |

| port ( A, B : IN std_logic; S, CO : OUT std_logic ); | ポート宣言(入出力信号と信号のデータタイプを定義) |

| end HALF_ADDER; | エンティティ終了。";"忘れるな! |

| architecture DATA_FLOW of HALF ADDER is | アーキテクチャ宣言 |

| signal C, D : std_logic; | 内部信号を定義 |

| begin C <= A or B ; D <= A nand B ; CO <= not D; S <= C and D; end DATAFLOW; |

同時処理文! コンピュータプログラムとは違う この場合4つの同時動作するゲートに対応 |

VHDLで用意されているデータタイプ(パッケージを呼ばずとも使える)

| Integer | 整数 | |

|---|---|---|

| Real | 浮動小数点 | 論理合成に使用できない |

| Bit | ロジック値 '0','1' | HiZ, Unknownが含まれずシミュレーションに向かない |

| Bit_vector | Bitのベクトルタイプ、例:"1001" | |

| Boolean | 論理値, FALSE, TRUE | |

| Character | ASCII文字 | 論理合成に使用できない |

| Time | 時間のレコードタイプ | 論理合成に使用できない |

| Natural, Positive | Naturalは0以上の整数、Positiveは1以上の整数 | |

| String | Characterのベクトルタイプ | 論理合成に使用できない |

| 'U' | Uninitialized | 'W' | Weak Unknown |

| 'X' | Unknown | 'L' | Weal Low |

| '0' | Low | 'H' | Weak High |

| '1' | High | '-' | Don't care |

| 'Z' | Hi-impedance |

Std_logicのベクタータイプ

これも同じくStd_logicのベクタータイプで、四則演算可能と非常に便利

上位 full_adder.vhd 下位 half_adder.vhd

component HALF_ADDER

port ( A, B : in BIT; S, CO : out BIT);

end component;

U0 : HALF_ADDER port map (A, B, U0_S, U0_CO);

U1 : HALF_ADDER port map (U0_S, CIN, S, U1_CO);

signal C : std_logic_vector (7 downto 0);

signal D : std_logic_vector (0 to 7);

C <= "10010101"; は左端が7ビット目で右端が0ビット目

D <= "11010101"; は左端が0ビット目で右端が7ビット目

●左端を最上位桁(MSB)とするようにすると、トラブリにくい。

signal A, B, C : std_logic_vector (3 downto 0);

C <= A and B;

と

C(3) <= A(3) and B(3);

C(2) <= A(2) and B(2);

C(1) <= A(1) and B(1);

C(0) <= A(0) and B(0);

は同じ意味。

signal A, B : std_logic_vector (3 downto 0);

signal C, D : std_logic_vector (7 downto 0);

C <= A & B;

D <= A(3) & A(3) & A(3) & A(3) & A;

signal A : std_logic;

signal B, C : std_logic_vector (7 downto 0);

B <= ('1', A, 5 downto 2 => '1', '0', A); -- B <= '1' & A & "11110" & A ; と同じ。

C <= (3 => '1', 5 => A, others => '0' ); -- C <= "00" & A & "01000"; と同じ。

signal A : std_log_vector (3 downto 0);

signal B : std_logic_vector (7 downto 0);

signal C : std_logic;

C <= A(3) ; --1ビットの取り出し

A <= B(3 downto 0) ; --4ビットの取り出し

以上