琉球大学情報工学科 和田 知久

前回やった順序回路では、フリップフロップに計算の途中の値を記憶させた。

今回はフリップフロップに状態を記憶させる有限状態マシンを設計する。

初期(電源投入時)のFFの値は不定であるので、注意を要する。通常はResetをかけて、初期値を設定する。

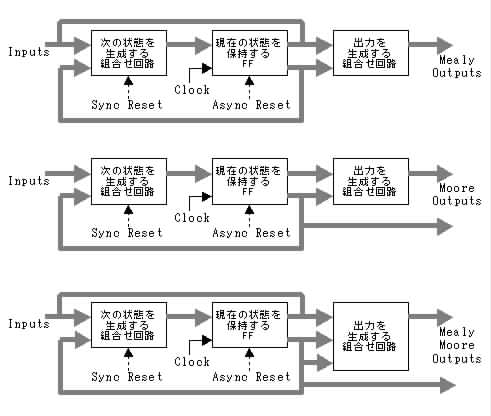

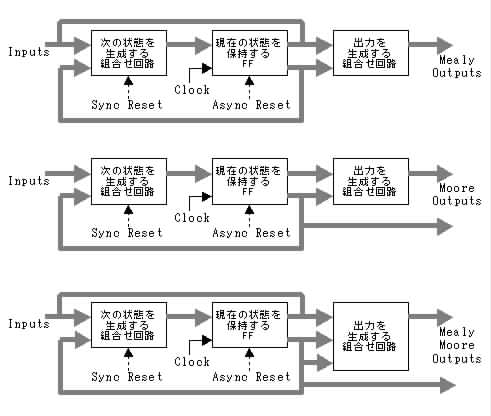

出力データの作り方により、MEALYとMOOREというタイプに分かれるが、基本的には、以下の図のように三つの機能を作ればよい。

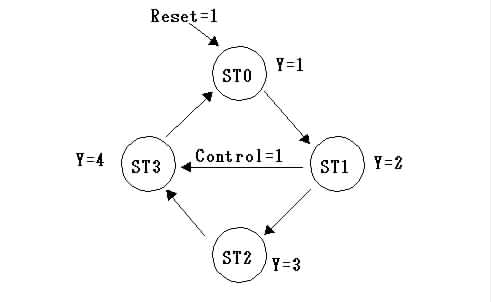

以下の4つの状態を遷移する。FSMの設計例3種類と、悪い例2種類を示す。

entity FSM21 is

port ( Clock, Reset : in std_logic;

Control : in std_logic;

Y : out integer range 0 to 4 );

end entity FSM21;

architecture RTL of FSM21 is

type StateType is (ST0, ST1, ST2, ST3);

signal CurrentState, NextState : StateType;

begin

----------------------

-- NEXT STATE

LOGIC

----------------------

COMB: process (Control, CurrentState)

begin

case CurrentState is

when ST0 => NextState <= ST1;

when ST1 =>

if (Control ='1') then NextState <=

ST2;

else NextState <= ST3;

when ST2 => NextState <= ST3;

when ST3 => NextState <= ST0;

when others => NextState <= ST0;

end case;

end process COMB;

----------------------

-- CURRENT STATE

LOGIC

----------------------

SEQ: process (Clock, Reset)

begin

if (Reset ='1') then CurrentState <= ST0;

elsif rising_edge(Clock) then CurrentState <=

NextState;

end if;

end process SEQ;

----------------------

-- OUTPUT LOGIC

(MOORE TYPE)

----------------------

with CurrentState select

Y <= 1 when ST0,

2 when ST1,

3 when ST2,

4 when ST3,

1 when others;

end architecture RTL;

entity FSM22 is

port ( Clock, Reset : in std_logic;

Control : in std_logic

Y :

out integer range 0 to 4);

end entity FSM22;

architecture RTL of FSM22 is

type StateType is (ST0, ST1, ST2, ST3);

signal STATE : StateType;

begin

---------------------

-- CURRENT & NEXT STATE LOGIC

---------------------

NEXT_CURR: process (Clock, Reset)

begin

if (Reset='1') then

STATE <= ST0;

elsif rising_edge(Clock) then

case (STATE) is

when ST0 => STATE <= ST1;

when ST1 =>

if (Control ='1') then STATE <=

ST2;

elsif STATE <= ST3;

end if;

when ST2 => STATE <= ST3;

when ST3 => STATE <= ST0;

when others => null;

end case;

end if;

end process NEXT_CURR;

----------------------

-- OUTPUT LOGIC

(MOORE TYPE)

----------------------

with CurrentState select

Y <= 1 when ST0,

2 when ST1,

3 when ST2,

4 when ST3,

1 when others;

end architecture RTL;

entity FSM23 is

port ( Clock, Reset : in std_logic;

Control : in std_logic;

Y : out integer range 0

to 4);

end entity FSM23;

architecture RTL of FSM23 is

type StateType is (ST0, ST1, ST2, ST3);

signal CurrentState, NextState : StateType;

begin

---------------------

-- NEXT & OUTPUT LOGIC

---------------------

COMB: process (Control, CurrentState)

begin

case CurrentState is

when ST0 =>

Y <= 1;

NextState <= ST1;

when ST1 =>

Y <= 2;

if (Control='1') then NextState <=

ST2;

else NextState <= ST3;

end if;

when ST2 =>

Y <= 3;

NextState <= ST3;

when ST3 =>

Y <= 4;

NextState <= ST0;

when others =>

Y <= 1;

NextState <= ST0;

end case;

end process COMB:

---------------------

-- CURRENT STATE LOGIC

---------------------

SEQ: process(Clock,Reset)

begin

if (Reset='1') then

CurrentState <= ST0;

elsif rising_edge(Clock) then

CurrentState <= NextState;

end if;

end process SEQ;

end architecture RTL;

entity FSM24 is

port ( Clock, Reset : in std_logic;

Control : in std_logic;

Y : out integer range 0

to 4 );

end entity FSM24;

architecture RTL of FSM24 is

begin

ALL_IN_1: process (Clock, Reset)

type StateType is (ST0, ST1, ST2, ST3);

variable State : StateType;

begin

if (Reset='1') then

State := ST0;

elsif rising_edge(Clock) then

case State is

when ST0 => State := ST1;

when ST1 =>

if (Control ='1') then State := ST2;

else State := ST3;

end if;

when ST2 => State := ST3;

when ST3 => State := ST0;

when others => State := ST0;

end case;

end if;

case State is

when ST0 => Y <=1;

when ST1 => Y <=2;

when ST2 => Y <=3;

when ST3 => Y <=4;

when others => Y <=1;

end case;

end architecture RTL;

entity FSM2BAD is

port (Clock, Reset : in std_logic;

Control : in std_logic;

Y : out integer range 1 to

4);

end entity FSM2BAD;

architecture RTL of FSM2BAD is

begin

ALL_IN_1: processor(Clock, Reset)

type StateType is (ST0, ST1, ST2, ST3);

variable STATE : StateType := ST0;

begin

if (Reset ='1') then

Y <= 1;

STATE := ST0;

elsif rising_edge(Clock) then

case (STATE) is

when ST0 => Y <= 1; -- elsif文の中で、Yに対してFFが生成。

STATE := ST1;

when ST1 => Y <= 2;

if (Control

='1') then

STATE :=

ST2;

else STATE :=

ST3;

end if;

when ST2 => Y <= 3;

STATE := ST3;

when ST3 => Y <= 4;

STATE := ST0;

end case;

end if;

end process ALL_IN_1;

end architecture RTL;