琉球大学情報工学科 和田 知久

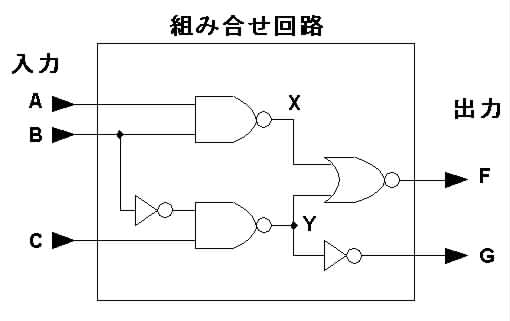

| 入力信号 | 途中の信号 | 出力信号 | ||||||

| A | B | C | X | Y | F | G | ||

| 0 | 0 | 0 | 1 | 0 | 0 | 1 | ||

| 0 | 0 | 1 | 1 | 1 | 0 | 0 | ||

| 0 | 1 | 0 | 1 | 0 | 0 | 1 | ||

| 0 | 1 | 1 | 1 | 0 | 0 | 1 | ||

| 1 | 0 | 0 | 1 | 0 | 0 | 1 | ||

| 1 | 0 | 1 | 1 | 1 | 0 | 0 | ||

| 1 | 1 | 0 | 0 | 0 | 1 | 1 | ||

| 1 | 1 | 1 | 0 | 0 | 1 | 1 | ||

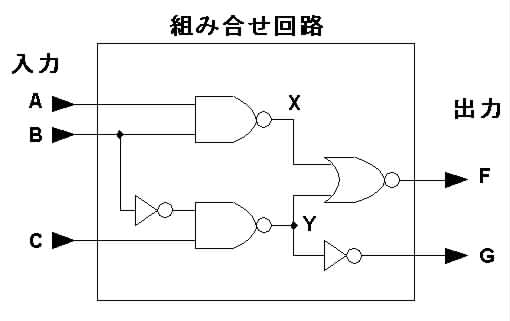

| F | AB | ||||

| C | 00 | 01 | 11 | 10 | |

| 0 | 0 | 0 | 1 | 0 | |

| 1 | 0 | 0 | 1 | 0 | |

| G | AB | ||||

| C | 00 | 01 | 11 | 10 | |

| 0 | 1 | 1 | 1 | 1 | |

| 1 | 0 | 1 | 1 | 0 | |

(例)

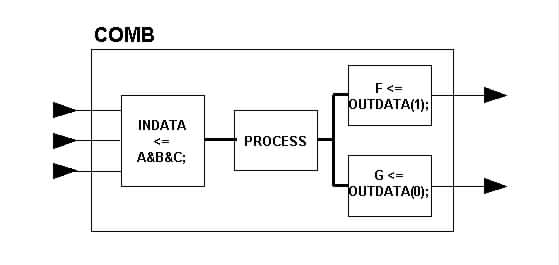

| 回路図のそのままの記述 | 簡単化後の回路そのままの記述 |

| library IEEE; use IEEE.std_logic_1164.all; entity COMB is architecture STRUCTURE1 of COMB is |

library IEEE; use IEEE.std_logic_1164.all; entity COMB is architecture STRUCTURE2 of COMB is |

(例: case文の使用)

| library IEEE; use IEEE.std_logic_1164.all; entity COMB is architecture RTL of COMB is |

|

| library IEEE; use IEEE.std_logic_1164.all; entity MUX4 is architecture RTL of MUX4 is |

|

signal A, B, C : std_logic;

A <= ( B <

C) ; -- これは違反

signal A : std_logic_vector (3 downto 0) ;

signal B :

std_logic_vector (2 downto 0) ;

A <= "1100" ---- 12

B <= "111"

---- 7

A > B --------> FALSE

signal C, D : std_logic_vector (0 to 3);

C <=

"1100" ---- 3

D <= "0111" ---- 14

C < D --------->

FALSE