今回は動作を見ることが目的すなわち、アルゴリズムを理解することが目的であるので、変数にはビット幅の指定はなく整数型でのシミュ-ションデモを紹介する。

以下にアルゴリズムデモのVHDLファイルをリンクする

/net/home/teacher/wada/public_html/cadpab/rsa_alg.vhd

にもファイルを置く。

| ライブラリ宣言 | library STD; use STD.TEXTIO.all; |

ファイルなどのI/O用のライブラリであるが、今回は使ってない。 |

| エンティティ宣言 | entity RSA_ALG is end entity RSA_ALG; |

こういう名前にしてみた |

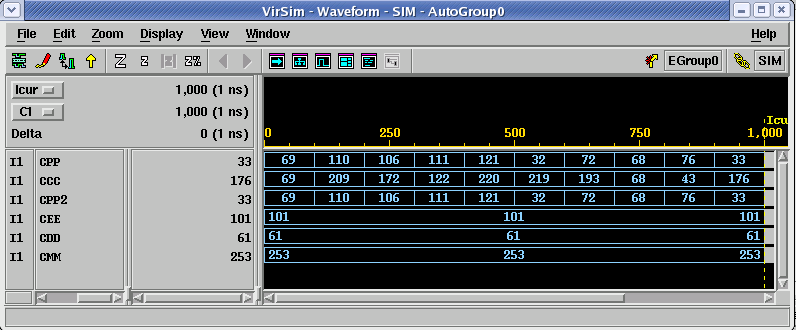

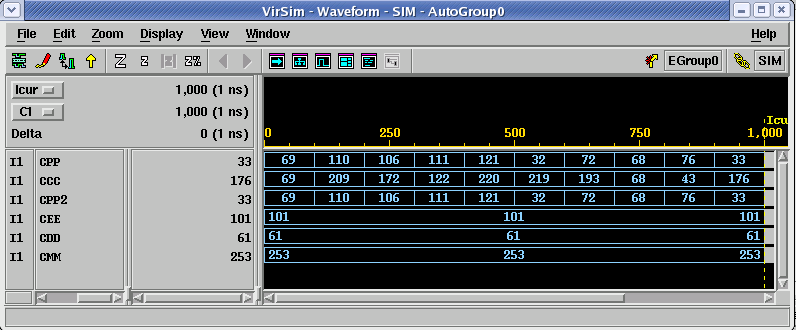

| アーキテクチャ宣言 | architecture ALG of RSA_ALG is type texttype is array (0 to 9) of integer; constant plaintext : texttype := ( 0 => 69, -- E 1 => 110, -- n 2 => 106, -- j 3 => 111, -- o 4 => 121, -- y 5 => 32, -- SP 6 => 72, -- H 7 => 68, -- D 8 => 76, -- L 9 => 33); -- ! constant CE : integer := 101; constant CD : integer := 61; constant CM : integer := 253; signal CPP, CEE, CDD, CMM, CCC, CPP2 : integer; begin |

送信する「Enjoy HDL!」のアスキーコードを整数のアレイで作成

整数10個のアレイをtesttypeという型を登録 定数としてplaintextに送信情報を初期値として用意。 その他係数も定数として用意した。 |

| SIG_GEN:process begin for I in 0 to 9 loop CPP <= plaintext(I); CEE <= CE; CDD <= CD; CMM <= CM; wait for 100 ns; end loop; end process SIG_GEN; RSA_ENC: process(CPP, CEE, CMM) variable TMP_v : integer; begin TMP_v := 1; for L in 1 to CEE loop TMP_v := (TMP_v * CPP) mod CMM; end loop; CCC <= TMP_v; end process RSA_ENC; RSA_DEC: process(CCC, CDD, CMM) variable TMP2_v : integer; begin TMP2_v := 1; for M in 1 to CDD loop TMP2_v := (TMP2_v * CCC) mod CMM; end loop; CPP2 <= TMP2_v; end process RSA_DEC; end architecture ALG; |

3つのプロセスを用意

1つめのSIG_GENは100nsおきに、送信データのplaintextを1文字ごとにCPP信号へ出す。 2つのRSA_ENCはCPPを受け取り、暗号化してCCCに結果を出す。 3つめのRSA_DECはCCCを受け取り、暗号を解読してCPP2へ解読結果を出す! 2番目と3番目は機能的には同じで、これに対応する合成可能な回路を設計すればよい! アルゴリズムは教科書P188の(8.24)式であり、最も回路規模が大きいものに対応し、改良が必要である。 | |

| configuration CFG_RSA_ALG of

RSA_ALG is for ALG end for; end CFG_RSA_ALG; |

いつものCONFIGURATION |

CPPは暗号化前アスキーデータ(10進数表示)

CCCは暗号化されたもの

CPP2は暗号解読されたもの

以上