琉球大学情報工学科 和田 知久

以下の手順に従って、与えられたVHDファイルを修正して、SCIROCCOシミュレーション、回路合成を行い、シミュレーション波形と、回路図をメイルにて送付する。

1) 以下の2つのファイルをコピーする。

以下はおなじファイルシステムからなので、以下をCPコマンドでコピーできる。

/net/home/teacher/wada/public_html/cadpub/mid1.vhd

/net/home/teacher/wada/public_html/cadpub/test_mid1.vhd

以下はWEBから取りたい人用

http://www.ie.u-ryukyu.ac.jp/~wada/cadpub/mid1.vhd

http://www.ie.u-ryukyu.ac.jp/~wada/cadpub/test_mid1.vhd

2)自分のID番号の下二桁をそれぞれa, bとする。

そして、以下の整数m,nを計算する。

m=mod(a+b, 15) +1;

n=mod(a*b, 15) +1;

注意: mod(x, 15)はxを15で割った余りで、0から14のどれかの値

m, nをそれぞれ4ビットの数に変換し、連接して8ビットに変換する。

以下の例では、75番を”1101 0110”に変換した例である。

m=mod(7+5, 15)+1=13=1101 (2進数)

n=mod(7*5, 15)+1=6=0110 (2進数)

上記8ビットを以下の赤字の部分に挿入して

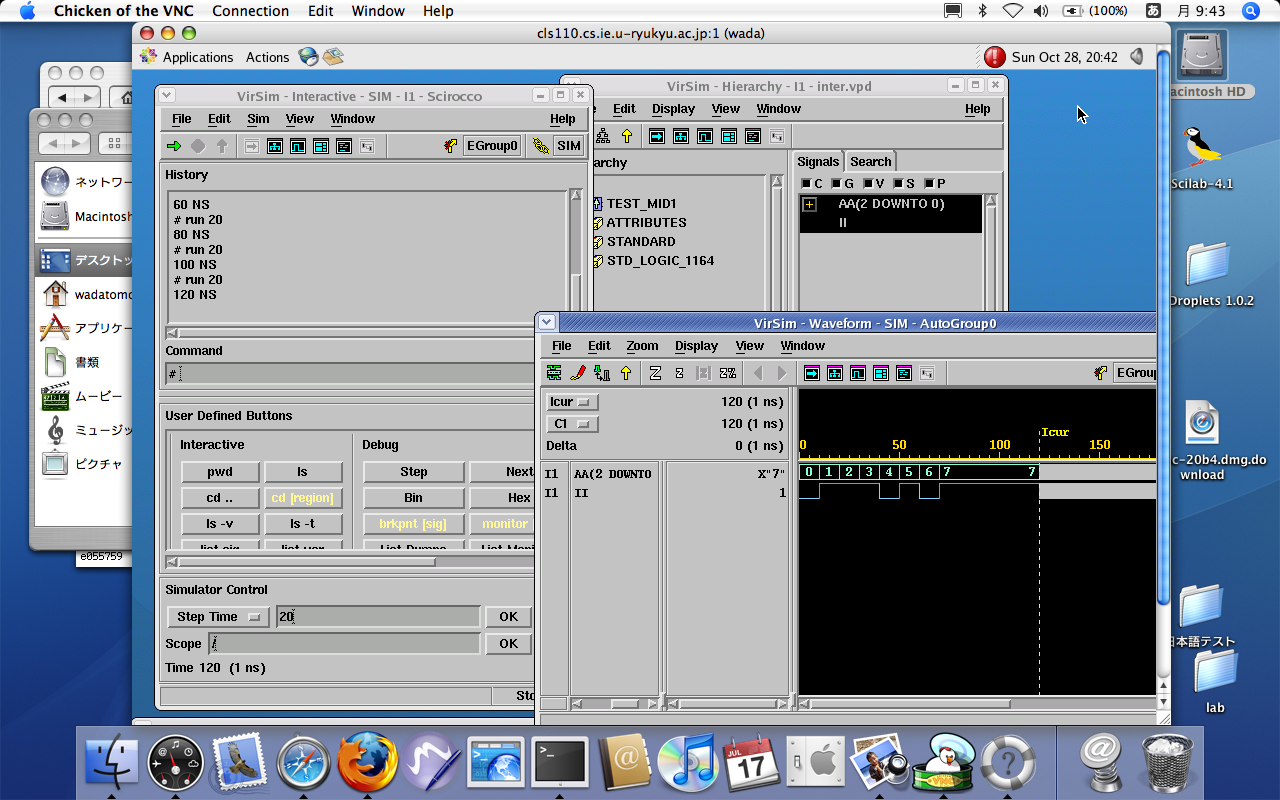

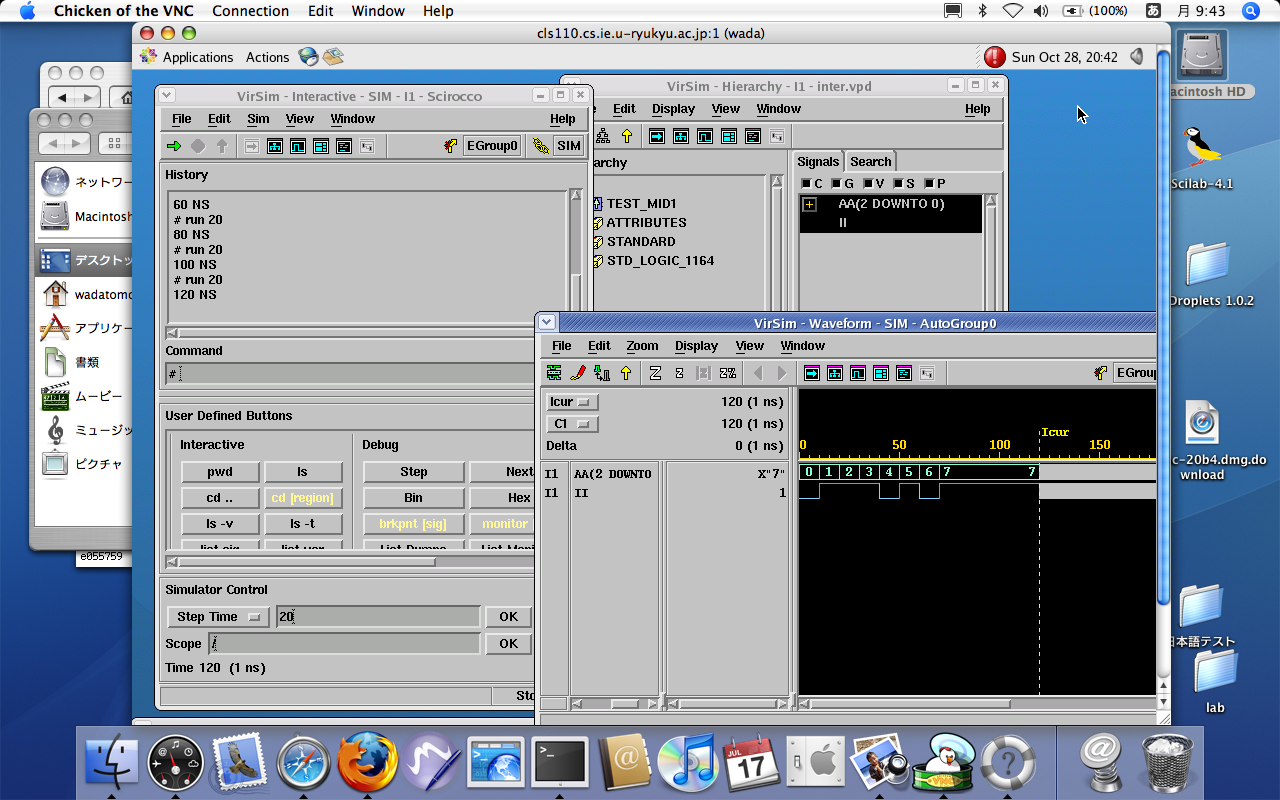

3) 変換したmid1.vhdとtest_mid1.vhdを用いてSCIROCCOシミュレーションを行い。

以下のようなスクリーンダンプを取れ!

以下のシミュレーション例は上記8ビットの値に対応していない。

スクリーンダンプは MACの画面で、コマンド - SHIFT - 3 で取ることができる。

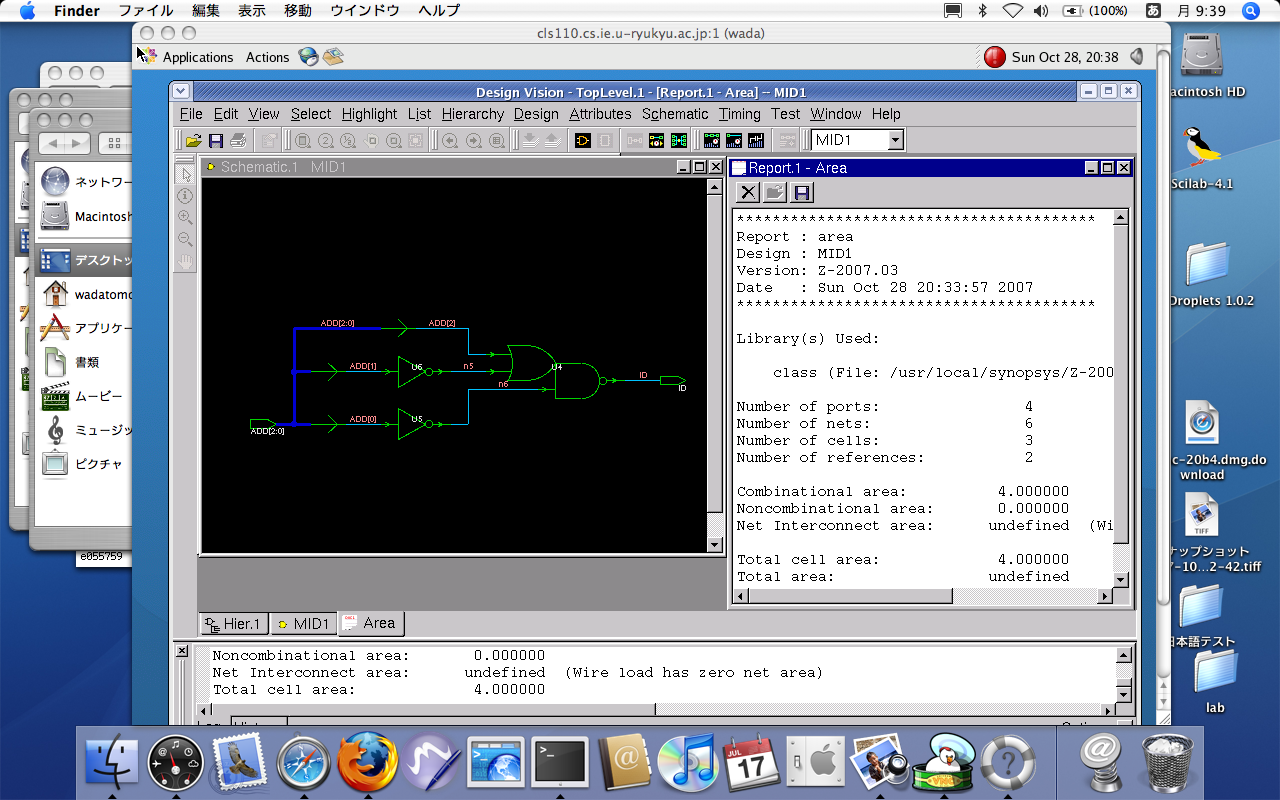

3) 変換したmid1.vhdを用いてdesign_viosnで回路合成を行い、面積レポートを表示して。

以下のようなスクリーンダンプを取れ!

以下の回路合成例は上記8ビットの値に対応していない。

5) メイルにて提出せよ!

提出先メイルアドレス: wada@ie.u-ryukyu.ac.jp

メイルタイトル(全て英数字で): cadmid1(学籍番号)

内容:

学籍番号

名前

上記2つの画面ダンプファイルの添付

以上