組み合せ回路のVHDL記述

琉球大学情報工学科 和田 知久

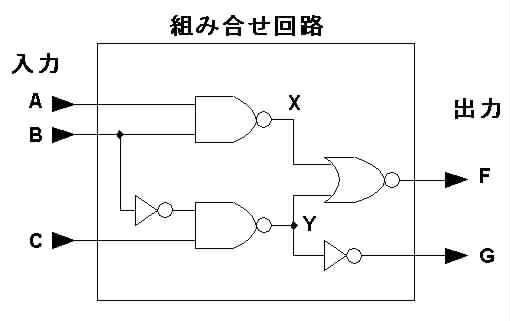

組み合せ回路の復習

· 組み合わせ回路とは ⇒ 出力信号の状態が入力信号のみで決定される回路。

· したがって以下の特性がある。

1. 真理値表で書ける。

2. 内部にラッチやレジスタのように値を保持する素子は含まれない

真理値表の復習

|

入力信号 |

|

途中の信号 |

|

出力信号 |

||||

|

A |

B |

C |

|

X |

Y |

|

F |

G |

|

0 |

0 |

0 |

|

1 |

0 |

|

0 |

1 |

|

0 |

0 |

1 |

|

1 |

1 |

|

0 |

0 |

|

0 |

1 |

0 |

|

1 |

0 |

|

0 |

1 |

|

0 |

1 |

1 |

|

1 |

0 |

|

0 |

1 |

|

1 |

0 |

0 |

|

1 |

0 |

|

0 |

1 |

|

1 |

0 |

1 |

|

1 |

1 |

|

0 |

0 |

|

1 |

1 |

0 |

|

0 |

0 |

|

1 |

1 |

|

1 |

1 |

1 |

|

0 |

0 |

|

1 |

1 |

これより、直接的にブール代数式で書ける!

F <= A and B and (notC) or A and B and C;

G <= notA and notB and notC or ......(省略)

カルノー図の復習

|

F |

AB |

||||

|

C |

|

00 |

01 |

11 |

10 |

|

0 |

0 |

0 |

1 |

0 |

|

|

1 |

0 |

0 |

1 |

0 |

|

ということで、 F <= A and B; と簡単化される。

|

G |

AB |

||||

|

C |

|

00 |

01 |

11 |

10 |

|

0 |

1 |

1 |

1 |

1 |

|

|

1 |

0 |

1 |

1 |

0 |

|

ということで、 G <= (notC) or B ; と簡単化される。

プロセス文を使わない組み合せ回路の記述

- プロセス文を使わないというのは、if文、case文、for-loop文などの順次処理文(ソフトウエアぽい高度な記述)を使えないということ。

- 結果的に回路図をそのまま記述したことになる。

(例)

|

回路図のそのままの記述 |

簡単化後の回路そのままの記述 |

|

library IEEE; entity COMB is architecture STRUCTURE1 of COMB is |

library IEEE; entity COMB is architecture STRUCTURE2 of COMB is |

· こんな記述では、設計の生産性は上がらない。

· 回路の簡単化はデザインコンパイラが行うので、設計者はもっと簡単に機能を記述すればよい。

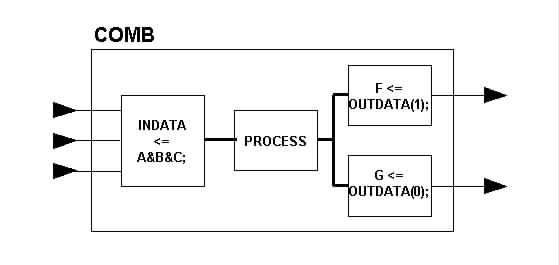

プロセス文を使う回路の記述

(例: case文の使用)

|

library IEEE; entity COMB is architecture RTL of COMB is |

|

プロセス文を使う回路の記述

· 上記記述にはprocess文を含めて4つの同時処理文があり、個別が並列に動作する。

· process文にはif文、case文、for-loop文などの順序処理文が記述できる。

· 組み合せ回路の生成にはセンシティビティリストにすべての入力を記述すし、case文やif文等ですべての場合を記述する。

· 要は入力の組み合せで出力が一義的に決まるように記述する。

if文を使う記述

|

library IEEE; entity MUX4 is architecture RTL of MUX4 is |

|

データタイプ Boolean と関係演算子

- 関係演算子は6種 = /= < <= > >=

- BOOLEANタイプ TRUE FALSE を返す。

- <= は信号代入と同じで、文脈で判断される。

signal A, B, C : std_logic;

A <= ( B < C) ; -- これは違反

- ビット長の異なる比較は、一番左のビットから比較をするので、注意!

signal A : std_logic_vector (3

downto 0) ;

signal B : std_logic_vector (2 downto 0) ;

A <= "1100" ---- 12

B <= "111" ---- 7

A > B --------> FALSE

- downto を使用しないと、比較が間違って判断される。

signal C, D : std_logic_vector (0

to 3);

C <= "1100" ---- 3

D <= "0111" ---- 14

C < D ---------> FALSE

以上