通常のデジタル回路はこのクロック信号の電圧レベルや、電圧の立ち上がりエッジなどを利用して一斉に動作する。このことを、クロックに同期して動作するという。

クロックの周期が 10ns (10ナノ時間) であれば、クロック周波数はその逆数であり、100MHzとなる。

PentiumIII 500MHzのパソコンでは、クロック周期は 2ns であり、2nsごとに新たな命令の実行を開始する。

通常のデジタル回路ではクロックに同期して(クロックの立ち上がりエッジごとに)、回路がなんだかの動作を行う。したがって、クロック周波数が高いほど(クロック周期が短いほど)高性能である。

| Dラッチの動作説明図 | Dラッチの動作波形 クロックHIGHではデータが転送 クロックLOWではデータ保持 |

|

|

| Dラッチのシンボル | Dラッチの回路図の一例 |

|

|

実際のDラッチの回路図

| Clock=’1’の時 | Clock=’0’の時 |

|

|

| Dフリップフロップの構成 Dラッチ2つで作れる |

Dフリップフロップの動作説明図 |

|

|

| クロック=’0’ LOWレベルの時 | クロック=’1’ HIGHレベルの時 |

|

|

| Dフリップフロップの動作波形 クロック立ち上がりエッジでデータを転送 その他の期間ではデータ保持 |

Dフリップフロップのシンボル 三角形がエッジトリガを示す |

|

|

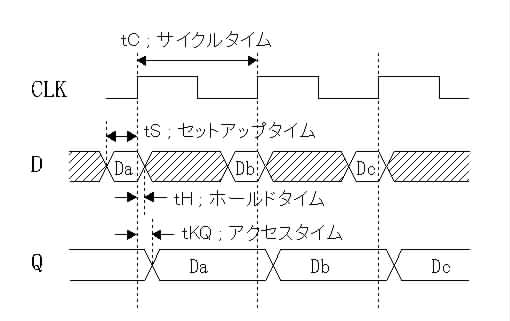

| シンボル | 名称 | 意味 |

| tC | サイクルタイム | 動作する周期、スペックでは最小値が規定される。 |

| tS | セットアップタイム | クロックエッジに対するデータを用意する時間、スペックでは最小値が規定される。 |

| tH | ホールドタイム | クロックエッジに対してデータを保持する時間、スペックでは最小値が規定される。 |

| tKQ | アクセスタイム | クロックエッジからデータ出力までの時間、スペックでは最大値が規定される。 |

宿題6 学籍番号 名前 日付 を書いて 提出すること。

1) 以下の波形をDラッチと、Dフリップフロップに入力した。それぞれの出力波形を示せ。

2) 上記1)と同じクロック、データ入力波形を以下のような、Dラッチ2段とD-FF2段の回路に入力した場合の出力端LB、FBの波形を示せ。LAとFAは上記1)に対応する。

3) 以下の回路の出力端LOUTとFOUTの動作波形を示せ。

但し、NOT回路の遅延時間は1ns、Dラッチ/D-FFの遅延時間を2ns、

クロックのサイクルタイムを20nsとし、

Dラッチ/D-FFの初期値(初期の出力値)を’0’とする。

4) 以下の回路の出力端OUT1とOUT2の動作波形を示せ。

OUT1とOUT2はある周期で同じ波形を繰り返す。

クロックの周期を10nsとすると、OUT1とOUT2の周期はいくらか?

5) 説明したように、デジタル回路ではD-FFを介して、組み合せ回路がデータの交換を

クロックの立ち上がりエッジに同期して行い、データ処理を行う。

2)の結果を復習して、以下の回路図のD-FFをDラッチに変更するとうまく

動作しないことを説明せよ。

以上