琉球大学 情報工学科 和田 知久

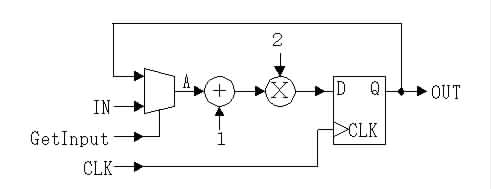

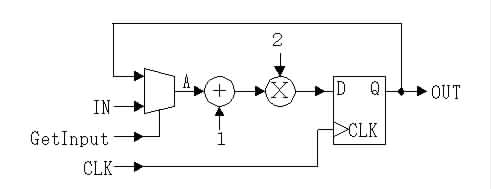

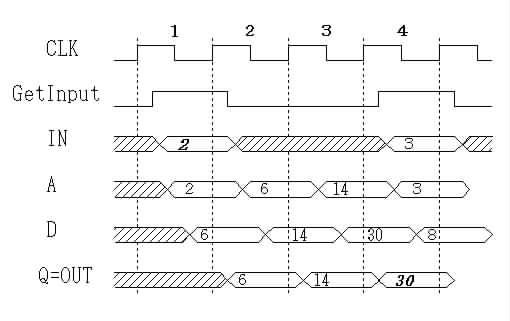

architecture RTL of ADDMUL

is

signal Q : unsigned (7 downto 0);

begin

process(Clk)

variable A : unsigned (7 downto 0);

begin

if rising_edge(Clk) then

----------

-- MUX

----------

MUX: if (GetInput = '1') then

A := Input;

else A := Q;

end if MUX;

----------

-- ADD1 & MUL2

----------

Q <= Shift_left((A + 1),1);

end if;

end process;

CLK信号は省略されている。

+記号はEXOR(排他的論理和)

上記のようなFFを直列に接続し、出力をフィードバックしたものをリニア・フィードバックシフトレジスタという。

単純ではあるが、色々な場所で用いられている。

1)携帯電話 CDMAのCにあたるCODE(擬似ランダムなシーケンス)の生成

2)データの暗号化と復号化

3)LSI内蔵テスト回路のランダムシーケンス生成

シフトレジスタのシフトの様子を以下に示す。周期15のシーケンスを繰り返す。この周期15の中で、0は7つで、1は8つで、これにより、擬似ランダムなシーケンスを生成できる。

1 0 0 0 0 1 0 0 0 0 1 0 0 0 0 1 1 1 0 0 0 1 1 0 0 0 1 1 1 1 0 1 1 0 1 0 0 1 0 1 1 1 1 0 0 1 1 1 1 1 1 1 1 0 1 1 1 0 0 1 1 0 0 0

以上