ここではx86プロセッサには出荷数量でおよばないが、それでもNintendo64やPlayStationそして多数のレーザプリンター等で用いられているRISC型MPUのMIPSプロセッサの一部の命令を実行するminimipsプロセッサを設計する。

** refer to the section 5.1-5.3 of Morgan Kaufmann

Publisher, "COMPUTER ORGANIZATION & DESIGN: the hardware

/ software interface 2nd", John L. Hennessy and David A.

Patterson

** 日経BP社「コンピュータの構成と設計」第2版、パターソン&ヘネシー、第5.1~5.3章参照

サポート命令

| 区分 | 命令 | 例 | 意味 | 備考 |

| 算術演算 | add | add R1,R2,R3 | R1 <= R2 + R3 | 加算 |

| subtract | sub R1,R2,R3 | R1 <= R2 - R3 | 減算 | |

| 論理演算 | and | and R1,R2,R3 | R1 <= R2 and R3 | 各ビットごとにAND |

| or | or R1,R2,R3 | R1 <= R2 or R3 | 各ビットごとにOR | |

| データ転送 | load word | lw R1, 100(R2) | R1 <= メモリ[R2+100] | メモリからレジスタへの転送 |

| store word | sw R1, 100(R2) | メモリ[R2+100] <= R1 | レジスタからメモリへの転送 | |

| 条件分岐 | branch on equal | beq R1,R2,25 | if (R1=R2) go to PC+4+100 | 等しい時にPC相対分岐 |

| set on less than | slt R1,R2,R3 | if (R2<R3) R1<=1 else R1<=0 | ||

| 無条件ジャンプ | jump | j 2500 | go to 10000 | 絶対アドレスジャンプ |

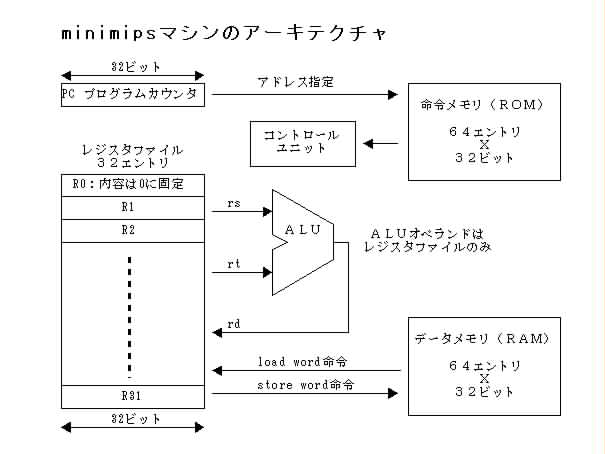

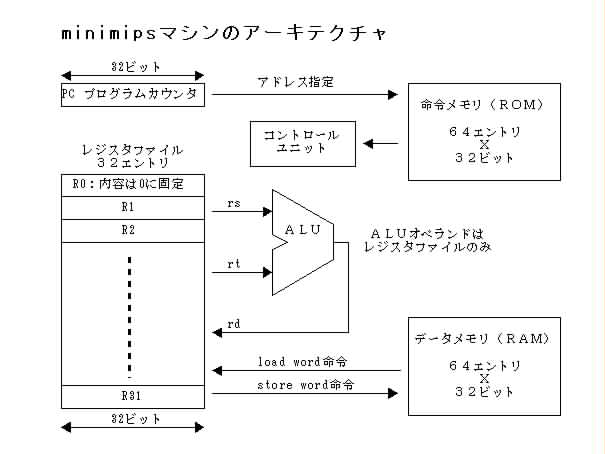

マシンアーキテクチャ

| 命令 | フォーマット名 | 例 | 備考 | |||||

| 6ビット | 5ビット | 5ビット | 5ビット | 5ビット | 6ビット | |||

| add | R形式 | 0 | 2 | 3 | 1 | 0 | 32 | add R1, R2, R3 |

| sub | 0 | 2 | 3 | 1 | 0 | 34 | sub R1, R2, R3 | |

| and | 0 | 2 | 3 | 1 | 0 | 36 | and R1, R2, R3 | |

| or | 0 | 2 | 3 | 1 | 0 | 37 | or R1, R2, R3 | |

| slt | 0 | 2 | 3 | 1 | 0 | 42 | slt R1, R2, R3 | |

| lw | I形式 | 35 | 2 | 1 | 100 | lw R1, 100(R2) | ||

| sw | 43 | 2 | 1 | 100 | sw R1, 100(R2) | |||

| beq | 4 | 1 | 2 | 25 | beq R1, R2, 25 | |||

| j | J形式 | 2 | 2500 | j 2500 | ||||

| フォーマット名 | 6ビット | 5ビット | 5ビット | 5ビット | 5ビット | 6ビット | 備考 |

| R形式 | op | rs | rt | rd | - | func | |

| I形式 | op | rs | rt | address | |||

| J形式 | op | address | |||||

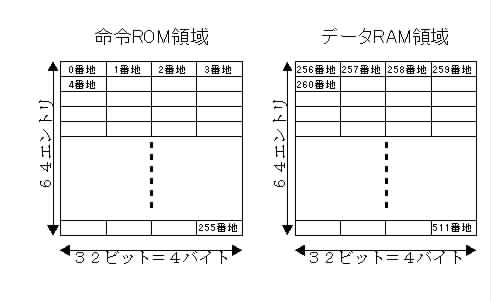

命令ROM irom.vhd

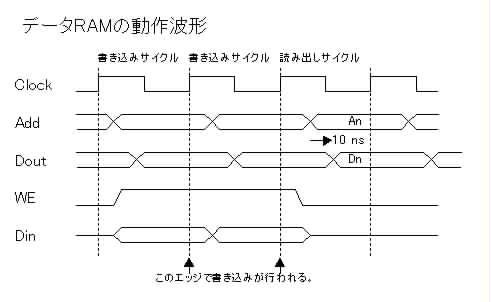

データRAM dram.vhd

使用パッケージ alu_pkg.vhd

テストベンチ test_minimips.vhd

作成するMPU minimips.vhd

entity IROM is

port ( Add : in unsigned (5

downto 0);

Dout :

out unsigned (31 downto 0) );

end entity IROM;

データRAMの内容

| データRAM | ソート後の内容 | |||||||||

| バイトアドレス | dramのAdd入力 | 00 | 01 | 10 | 11 | 00 | 01 | 10 | 11 | |

| 256 | 0 | 0 | -> | 7 | ||||||

| 260 | 1 | 1 | -> | 6 | ||||||

| 264 | 2 | 2 | -> | 5 | ||||||

| 268 | 3 | 3 | -> | 4 | ||||||

| 272 | 4 | 4 | -> | 3 | ||||||

| 276 | 5 | 5 | -> | 2 | ||||||

| 280 | 6 | 6 | -> | 1 | ||||||

| 284 | 7 | 7 | -> | 0 | ||||||

| ... | ||||||||||

| 384 | 32 | 256 | 256 | |||||||

| 388 | 33 | 32 | 32 | |||||||

| 392 | 34 | 4 | 4 | |||||||

| ... | ||||||||||

命令ROMの内容

| 命令ROMの内容 | ||||||

| バイトアドレス | iromのAdd入力 | 00 | 01 | 10 | 11 | 説明 |

| 0 | 0 | NOP | ||||

| 4 | 1 | NOP | ||||

| 8 | 2 | LW R1, 388(R0) | R1 <= 32 | |||

| 12 | 3 | LW R2, 384(R0) | R2 <= 256, 先頭番地 | |||

| 16 | 4 | LW R3, 392(R0) | R3 <= 4 | |||

| 20 | 5 | ADD R5, R1, R2 | R5 <= 288, 最終番地の次 | |||

| 24 | 6 | SUB R5, R5, R3 | R5 <= R5 - 4 = 284, 最終番地 | |||

| 28 | 7 | ADD R6, R2, R0 | R6 <= R2 = 256 転送、R0は0固定 | |||

| 32 | 8 | ADD R7, R6, R0 | R7 <= R6、比較するデータ1のアドレス | |||

| 36 | 9 | ADD R8, R7, R3 | R8 <= R7 + 4、比較するデータ2のアドレス | |||

| 40 | 10 | LW R10, 0(R7) | R10 <= 比較するデータ1 | |||

| 44 | 11 | LW R11, 0(R8) | R11 <= 比較するデータ2 | |||

| 48 | 12 | SLT R9, R10, R11 | R10 < R11ならR9 <= 1、違うならR9 <=0 | |||

| 52 | 13 | BEQ R9, R0, +2 | R9が0ならばPC=PC+4+2*4=64へ分岐 | |||

| 56 | 14 | SW R10, 0(R8) | 比較データ1をスワップしてメモリへ | |||

| 60 | 15 | SW R11, 0(R7) | 比較データ2をスワップしてメモリへ | |||

| 64 | 16 | ADD R7, R7, R3 | R7 <= R7 +4, アレイインデックスを進める | |||

| 68 | 17 | BEQ R7, R5, +1 | インデックスが最終アドレスならLOOP1を抜ける | |||

| 72 | 18 | J 9 | 9番地へジャンプ、LOOP1 | |||

| 76 | 19 | SUB R5, R5, R3 | R5 <= R5 - 4, 最終番地を下げる。ここに最小値がある。 | |||

| 80 | 20 | BEQ R5, R2, +1 | 最終番地が先頭番地と一致するとLOOP2を抜ける。 | |||

| 84 | 21 | J 8 | 8番地へジャンプ、LOOP2 | |||

| 88 | 22 | NOP | ||||

entity DRAM is

port ( Add : in

unsigned (5 downto 0);

Clock

: in std_logic;

WE : in std_logic;

Din

: in unsigned (31 downto 0);

Dout

: out unsigned (31 downto 0) );

end entity DRAM;

entity MINIMIPS is

port ( Clock : in std_logic;

Reset : in

std_logic; -- reset when it is '1'

Iadd : out

unsigned (5 downto 0); -- Address for IROM

Inst : in

unsigned (31 downto 0); -- Instruction from IROM

Dadd : out

unsigned (5 downto 0); -- Address for DRAM

WE :

out std_logic; -- DRAM Write Enable

Wtdata : out

unsigned (31 downto 0); -- Write data to DRAM

Rddata : in

unsigned (31 downto 0) ); -- Read data from DRAM

end entity MINIMIPS;