VLSI 2012 FINAL TASK

2013/01/08

琉球大学工学部情報工学科 和田 知久

最終課題は、講義で説明したSRPプロセッサシステムを改良し、4点DFTもしくは8点DFTを

アセンブラーコードにて実行できるようにする。

入力の4点(もしくは8点)は、複素数sr + j*si で、sr、siはそれぞれ16ビットとし、srとsiを連接して32ビットとして、主記憶に記憶する。

したがって、4点の場合は、主記憶上の32ビット変数4個(8点の場合は8個)が入力となる。

sr, siは各16ビットであるが、以下のように小数点の位置があると仮定する。最上位ビットMSBは符号を表し、値としては-1以上1未満の数を表すとする。

|

固定小数点フォーマット |

例1 |

例2 |

|

SXXX XX . XX XXXX XXXX |

0000

00 .10 0000 0000 = 0.5(10進数) |

1111

11. 10 0000 0000 = -0.5(10進数) |

*** 小数点の位置を当初から変更している 注意! 注意! ***

4点DFT(もしくは8点DFT)の出力も上記と同様なフォーマットとし、結果を主記憶に出力する。

[0] LEVEL0 TASK

レベル0タスクは、2つの複素数をメモリ上に用意し、その2つの乗算結果の複素数をメモリ上に出力する。

この動作をするアセンブラーコードをROM上に作成し、

プロセッサの機能として、32ビットどうしの乗算命令やシフト命令などを必要に応じて追加し、

RAM上に記憶した入力データに対して、プログラムを実行し、乗算結果をRAM上に出力する。

[1] LEVEL1 TASK

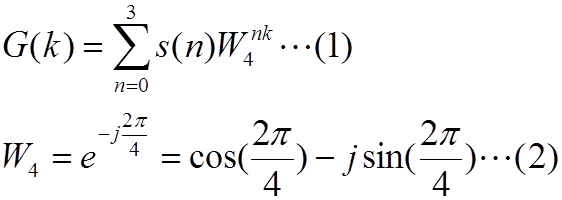

入力s(0), s(1), s(2), s(3)は4つの複素数入力であり、以下の式(1)、(2)にしたがって、G(0), G(1), G(2), G(3)なる複素数を計算する。

この動作をするアセンブラーコードをROM上に作成し、

プロセッサの機能として、32ビットどうしの乗算命令やシフト命令などを必要に応じて追加し、

RAM上に記憶した入力データに対して、プログラムを実行し、4点DFT結果をRAM上に出力する。

COSやSINの値が必要であれば、必要に応じて、値をRAM上に用意すること。

[2] LEVEL2 TASK

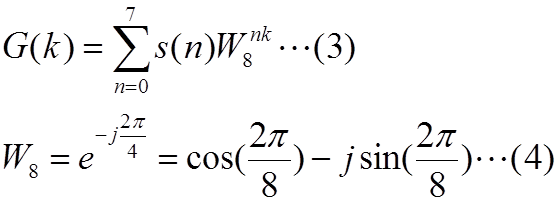

入力s(0), s(1), s(2), s(3), s(4), s(5), s(6), s(7)は8つの複素数入力であり、以下の式(3)、(4)にしたがって、G(0), G(1), G(2), G(3), G(4), G(5), G(6), G(7)なる複素数を計算する。

この動作をするアセンブラーコードをROM上に作成し、

プロセッサの機能として、32ビットどうしの乗算命令やシフト命令などを必要に応じて追加し、

RAM上に記憶した入力データに対して、プログラムを実行し、4点DFT結果をRAM上に出力する。

COSやSINの値が必要であれば、必要に応じて、値をRAM上に用意すること。

[3] レポート採点基準

上位レベルのTASKを実現するほど高得点を与える。

レポートには、ROM内のアセンブラーコードとその説明、

プロセッサに追加した命令の説明、RAMの使用法を明記すること。

特に、VLSI設計の講義であるので、プロセッサに追加した、命令により、プロセッサの回路規模がどのように変化したかを明記せよ。

[4] レポート提出期限

友人たちと協力してレポートを仕上げてもよいし、個人的にレポートを仕上げてもよいが、

レポートは個人として提出すること。

提出期限は 2月12日火曜17:00とする。

メイルにて、和田まで提出すること。

優秀レポート提出者には、3月末の発表会での発表をお願いし、賞品を贈呈する予定。

[5] 今後の予定

1/15, 1/22 の講義時間の前半にて、設計ヒントを順次説明する。各講義時間の後半は、各自の設計実習としてレポート課題を進めてください。

質問などは、講義時間に受け付けます。

以上