2.7 順序回路の記述 (教科書P44あたり)

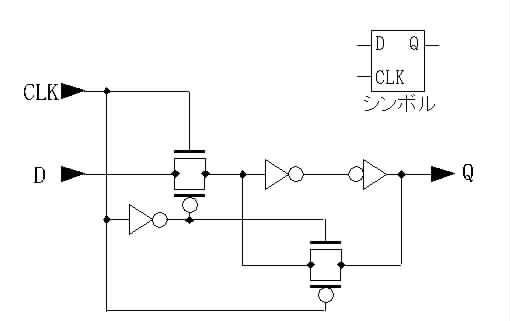

ラッチの定義(例:Dラッチ)

- クロック入力がアクテイブ(たとえばHIGH)の時、入力から出力へデータが転送され、

- クロック入力が非アクテイブ(たとえばLOW)の時、データは前の状態を保持する。

- 下記はDラッチの例である。

CLKがHighの時に、入力Dは出力Qへインバータ2段で接続され、

CLKがLowの時に、インバータ2段がリング接続になり、値を保持する。

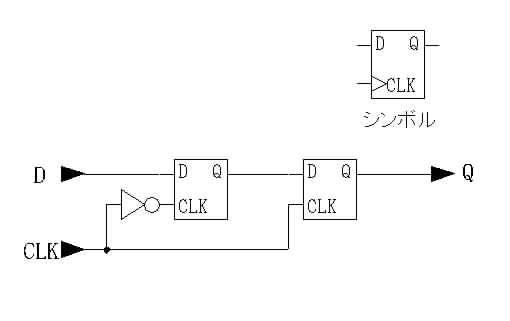

Dフリップフロップ(FF)の定義(例:Dフリップフロップ)

- クロック入力が非アクテイブからアクテイブへ(たとえばLow->High)の変化時に、入力Dからデータが取りこまれ、出力Qへデータが転送される。

- 出力はクロックのLow->High変化時のみ変化する。

- 下記はDラッチ2つで構成された、ポジティブトリガのDFFの例である。

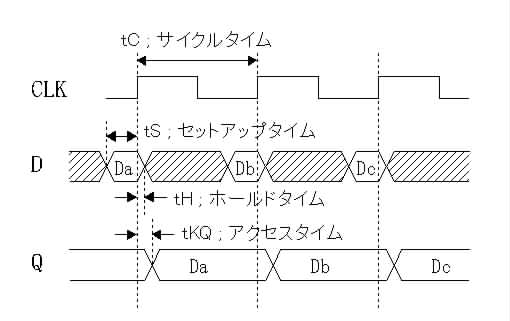

フリップフロップ(FF)の動作波形

- クロック(CLK)入力の立ち上がり変化時にのみデータ入力(D)を取りこみ、内部状態を更新する。この内部状態はデータ出力(Q)に出力される。

|

シンボル |

名称 |

意味 |

|

tC |

サイクルタイム |

動作する周期、スペックでは最小値が規定される。 |

|

tS |

セットアップタイム |

クロックエッジに対するデータを用意する時間、スペックでは最小値が規定される。 |

|

tH |

ホールドタイム |

クロックエッジに対してデータを保持する時間、スペックでは最小値が規定される。 |

|

tKQ |

アクセスタイム |

クロックエッジからデータ出力までの時間、スペックでは最大値が規定される。 |

VHDLにおけるフリップフロップ(FF)の生成方法

教科書 2.7 (P44)

リスト2.11: RESETのないD−FF記述 (1)

リスト2.12: RESETのないD−FF記述 (2)

リスト2.13: 非同期RESETのあるD−FF記述

リスト2.14: 非同期SET・RESETのあるD−FF記述

リスト2.15: 同期RESETのあるD−FF記述

移動平均回路の設計

- 以下の回路は8ビットの入力信号を移動平均する回路である。

- 入力からクロックサイクルごとに入力されてくる信号のうち、最新の4個の入力値をすべて加算し、4で割ることによりその平均値を出力する。

移動平均回路のVHDL記述

|

ライブラリ宣言 |

library IEEE; |

今回は入力信号として、2の補数表現を用いた正・負混合の信号を用いるので、P63コラム4の算術演算用パー-ケージで説明されているように、std_logic_arithを用いる。 |

|

エンティティ宣言 |

entity AVG4

is |

クロック入力:CLK データ出力:AVGOUT(8ビット) |

|

アーキテクチャ宣言 |

architecture RTL of AVG4

is |

4つのFF出力を定義 加算した信号を定義 |

|

-- SHIFT

REGISTER |

このような記述で4つのFFが生成される。 FF1 :=FMINPUT; とすると、 FF4 :=FMINPUT; と等価となり、FFは1個しか生成されない。 | |

|

-- SUM |

std_logic_arithを用いているので、P63コラム4の算術演算用パー-ケージで説明されているように、signedで型変換を行っている。 8ビットを10ビットに拡張する時に、”00”を前につけると、全て正の数になってしまうので、MSBを2ビットコピーしている。 | |

|

-- DIVIDE BY 4 (SHIFT 2 bit),

OUTPUT REGISTER |

出力のレジスタを記述している。 4の割り算を2ビット右シフトで実現している。 ここでは、四捨五入は用いず、切り捨てしている。 |

テストベンチのVHDL記述

|

ライブラリ宣言 |

library STD, IEEE; |

教科書P85にTEXTIOパッケージの説明がある。 今回、テスト入力として他のテキストファイルに書かれた値を用いるので、ライブラリSTDを指定し、パッケージTEXTIOを呼び出している。 |

|

エンティティ宣言 |

entity TESTBENCH_FF1

is |

テストベンチであるので、中味は空である。 |

|

アーキテクチャ宣言 |

architecture SIM_DATA of

TESTBENCH_FF1 is |

今回テストされるAVG4回路(移動平均回路)をコンポーネント(部品)宣言している。 その他用いる信号を宣言している。 |

|

-- Sysetem CLK generation |

システムクロックを発生している。 5nsごとに変化するので、クロック周期は10nsである。 CLKの初期値はsignal宣言のところで、定義されている。 | |

|

-- DUT |

テストされる回路AVG4を置いている。 | |

|

-- TEST VECTOR end SIM_DATA; |

詳しくは、P85ページの説明とP87ページのリスト4.14を参考にしてください。 fm.txt の値を読み込んで、10nsすなわち、毎サイクルごとに値をFMINPUT信号に代入している。 if文は終了条件。 | |

|

configuration CFG_FF1 of

TESTBENCH_FF1 is |

VHDLではひとつのエンティティに複数のアーキテクチャを |

実習 移動平均回路の動作シミュレーション(1)

0) 作業ディレクトリに、上記3つのファイルをコピーする。

1) 正常動作を確認せよ!

2) 回路の合成を行え

HomeWork3

1) 上記内容をレポートにして提出せよ!

2) 16点平均をとる回路に再設計し、動作波形を示し、上記4点平均回路との回路規模を比較せよ。

以上